模擬CMOS集成電路設(shè)計(jì)是電子工程領(lǐng)域的核心技能之一,廣泛應(yīng)用于通信、傳感器、電源管理等系統(tǒng)。對(duì)于初學(xué)者而言,掌握以下16個(gè)關(guān)鍵學(xué)習(xí)要點(diǎn),能夠幫助您系統(tǒng)性地建立知識(shí)框架,逐步深入這一領(lǐng)域。

- 半導(dǎo)體物理基礎(chǔ):理解MOSFET的工作原理,包括載流子運(yùn)動(dòng)、閾值電壓、溝道形成等基本概念,這是所有設(shè)計(jì)的基石。

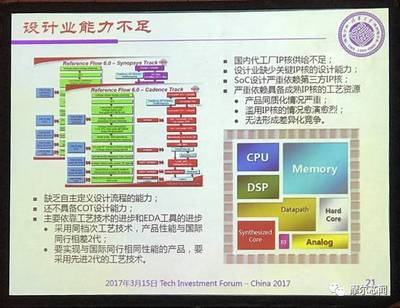

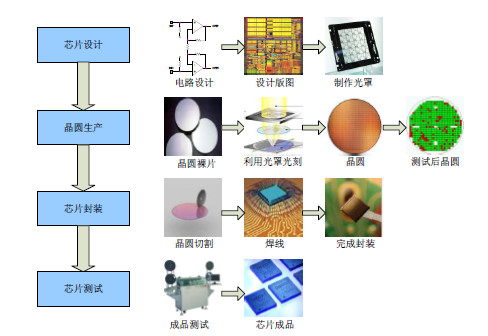

- CMOS工藝技術(shù):熟悉CMOS制造流程,如光刻、摻雜、氧化等步驟,了解工藝參數(shù)對(duì)器件性能的影響。

- 器件模型與特性:學(xué)習(xí)MOSFET的直流和交流模型(例如SPICE模型),掌握跨導(dǎo)、輸出電阻、電容等關(guān)鍵參數(shù)。

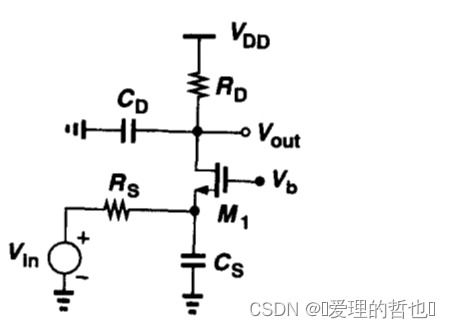

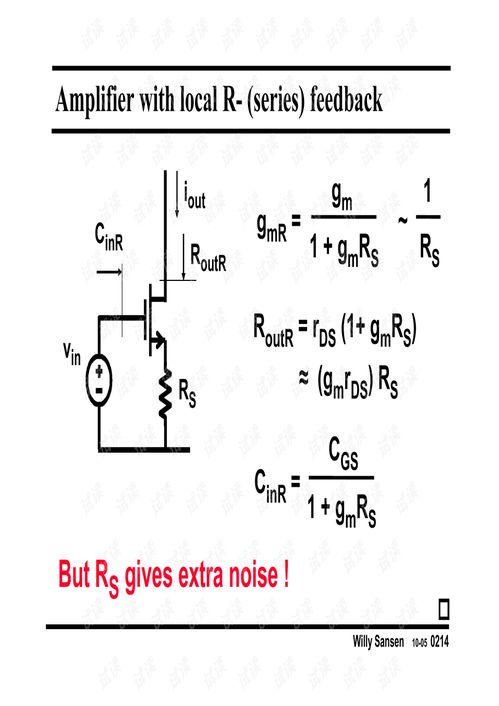

- 單級(jí)放大器設(shè)計(jì):從共源、共柵、共漏等基本放大器結(jié)構(gòu)入手,分析其增益、帶寬、輸入輸出阻抗等性能。

- 差分放大器:理解差分對(duì)的工作原理,掌握共模抑制比(CMRR)、失調(diào)電壓等概念,這是模擬電路中的核心模塊。

- 電流鏡與偏置電路:學(xué)習(xí)如何設(shè)計(jì)穩(wěn)定的電流源和偏置網(wǎng)絡(luò),確保電路在各種條件下正常工作。

- 頻率響應(yīng)分析:使用極點(diǎn)、零點(diǎn)概念分析電路的頻率特性,理解帶寬和穩(wěn)定性的設(shè)計(jì)方法。

- 噪聲分析:掌握熱噪聲、閃爍噪聲等來源,學(xué)習(xí)如何計(jì)算和優(yōu)化電路的噪聲性能。

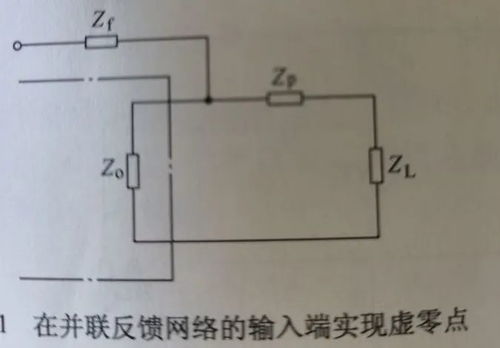

- 反饋理論:理解負(fù)反饋對(duì)增益、帶寬、線性度的影響,設(shè)計(jì)穩(wěn)定的反饋網(wǎng)絡(luò)。

- 運(yùn)算放大器設(shè)計(jì):綜合運(yùn)用前述知識(shí),設(shè)計(jì)高性能運(yùn)放,關(guān)注增益、相位裕度、壓擺率等指標(biāo)。

- 比較器與振蕩器:學(xué)習(xí)非線性電路的設(shè)計(jì),如比較器的遲滯特性,以及LC、環(huán)形振蕩器的原理。

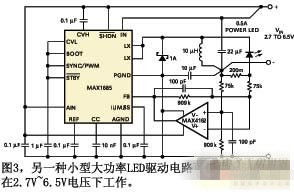

- 數(shù)據(jù)轉(zhuǎn)換器基礎(chǔ):了解ADC和DAC的基本類型(如逐次逼近型、Sigma-Delta型),掌握其精度和速度的權(quán)衡。

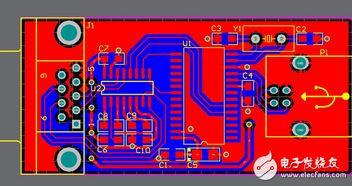

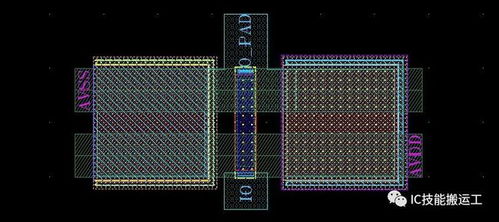

- 版圖設(shè)計(jì):學(xué)習(xí)物理設(shè)計(jì)規(guī)則,匹配、屏蔽、寄生效應(yīng)等版圖技巧,確保電路可制造且性能達(dá)標(biāo)。

- 仿真工具使用:熟練運(yùn)用SPICE類工具(如Cadence、HSPICE)進(jìn)行電路仿真,驗(yàn)證設(shè)計(jì)功能。

- 測(cè)試與驗(yàn)證:掌握測(cè)試方法,分析實(shí)際芯片與仿真結(jié)果的差異,進(jìn)行調(diào)試和優(yōu)化。

- 系統(tǒng)級(jí)思考:將電路模塊集成到更大系統(tǒng)中,考慮功耗、面積、成本等整體優(yōu)化因素。

學(xué)習(xí)模擬CMOS集成電路設(shè)計(jì)需要理論結(jié)合實(shí)踐。建議從教科書(如拉扎維的《模擬CMOS集成電路設(shè)計(jì)》)入手,配合仿真練習(xí)和簡(jiǎn)單項(xiàng)目,逐步積累經(jīng)驗(yàn)。隨著技術(shù)進(jìn)步,持續(xù)關(guān)注新工藝和設(shè)計(jì)方法,才能在這一領(lǐng)域不斷深入。